疫情导致的金融波动让数字货币市场逐步回暖,BTC的价格起伏不定,而关于减半的话题讨论热烈,这其中蕴含着诸多值得深思的议题。

数字货币市场的复苏态势

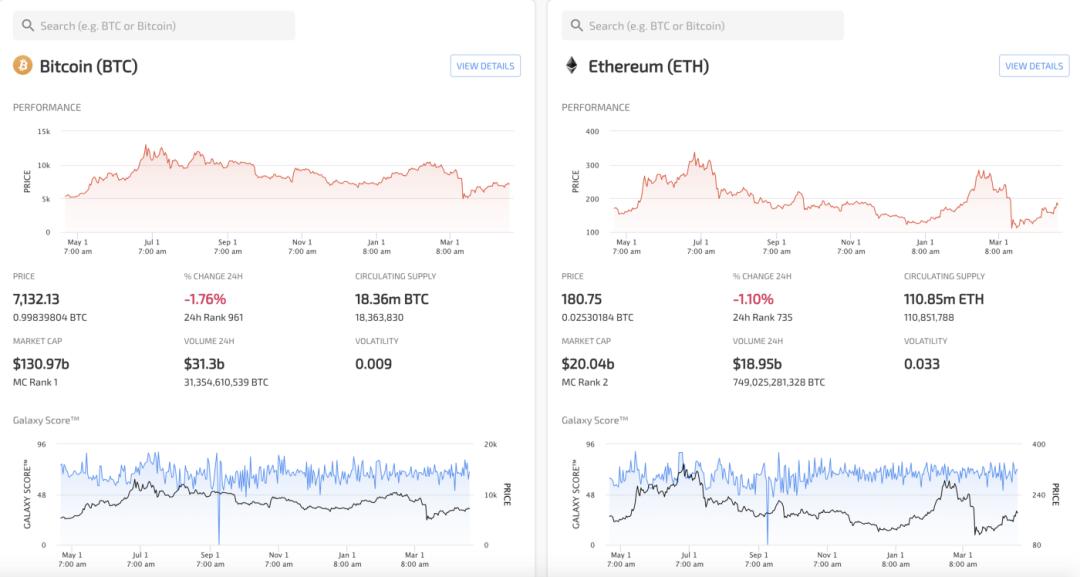

新冠疫情对数字货币市场造成了冲击,一度使其陷入低谷。那时,投资情绪普遍低迷,交易活跃度显著减少。但随着全球疫情逐步得到控制,经济开始显现复苏迹象,数字货币市场正逐步回暖。比如,BTC价格回升至7000美元以上,这无疑是一个积极的信号。这一变化不仅关乎投资者信心,还与全球金融趋势紧密相连。各种数字货币的表现各异,ETH在经历暴跌后也有所反弹,这些都表明市场正在摆脱低谷。

每个阶段的数字货币市场走势都有其独特之处。先前,全球各国在应对疫情时采取了不同的策略,部分国家采取了较为宽松的政策,支持金融创新模式,这为数字货币带来了一定的机遇。然而,某些保守地区的发展相对滞后。因此,数字货币市场的回暖是由多种因素共同促成的,包括地域差异、政策调控的松紧程度以及公众投资观念的变化。

BTC减半及其对市场的影响

BTC减半事件并不少见,2012年和2016年都曾出现。2012年减半时,每周BTC产出价值减少了30.2万美元;2016年减半后,这一数字增至819万美元。到了2020年,每周的BTC产出价值预计将减少至6300万美元。根据历史数据,BTC减半后价格总会出现波动。减半意味着供应量下降,按照经济原理,供应减少可能导致价格上涨。然而,市场的复杂性使得价格走势难以准确预测。

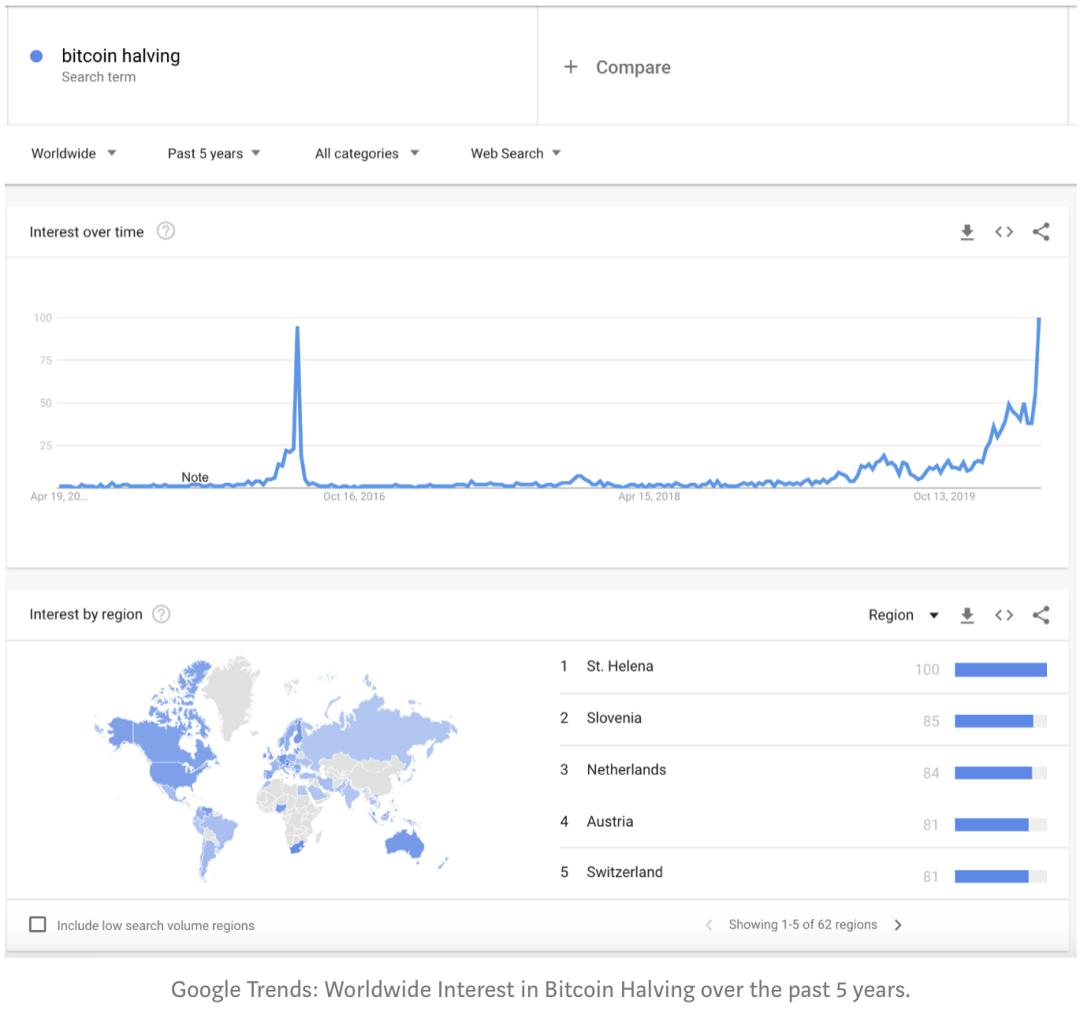

市场供应的减少,是否必然导致需求上升并推高价格,这是一个不明确的议题。以2020年为例,BTC减半的搜索量已经超过了2016年,大家对此都十分关注。但如果只根据供应量来推测需求,很容易忽视其他关键因素,例如公众的投资跟风心理或国际金融政策等。

BTC价格与社交量关系

过去一年,BTC的社交活动量维持了稳定状态,但近期呈现上升趋势。特别是在2020年3月20日,这一增长尤为明显。社交活动量是衡量社区活跃度的重要标准,它与价格变动存在关联。一般来说,社交活动量上升可能表明更多人开始关注,但这并不意味着价格一定会上涨。例如,先前的研究发现,BTC的看涨情绪与社交活动量的增加是同步的,但看跌情绪并未出现相应的峰值。在许多情况下,公众情绪会在网络上迅速传播并被放大,但数字市场有其固有的规律,并非完全受情绪所左右。

自2016年起,数字货币市场中的BTC价格话题在社交平台上热度波动明显。世界各地对BTC的看法各异。比如,日本对数字货币的接受度较高,社交讨论多偏向正面,推动价格上涨;而某些欧洲国家监管严格,社交讨论有时会变成对价格的负面影响。

BTC价格的走势波动

BTC的价格在6600到7300美元间波动不定,暂未显现出明显的趋势。自“黑色星期四”的金融动荡后,略有回升。以4月3日为例,BTC就保持在那个价格区间。这个区间的形成是众多投资者买卖行为的结果。投资者的心理状态对此影响颇大。一些经济学家指出,投资者的恐慌或贪婪心态常导致价格与价值不符。

总体趋势来看,若BTC未能突破4月初所面临的7400美元的阻力,其价格或许会回升到7900至8000美元的范围。然而,目前金融市场动荡不安,全球经济政策和疫情发展等因素都可能随时左右投资者的情绪。因此,BTC的价格走势仍然存在诸多不确定性。

ETH与BTC的对比表现

ETH和BTC在价格变动方面存在不同。撰写本报告时,ETH的价格下跌至182美元,跌幅为2.79%。其第一支撑位在176美元,同时也是上周的高点。与BTC价格波动不定、难以预测走势相比,ETH在“黑色星期四”暴跌后,价格回升至190美元,已完全恢复。尽管ETH和BTC都是数字货币,并受到相同市场大环境的影响,但由于它们的技术特性、用户群体特征等因素,表现上存在差异。

全球投资者对区块链等新技术中的数字货币表现出浓厚兴趣,其中一部分人看重ETH在技术革新方面的潜力,而另一部分人则更信赖BTC的市场稳定性。这种不同的投资偏好,进而对ETH和BTC的价格变动及市场表现产生了影响。

对加密社区的短期影响

现在,只要比特币价格未超过7000美元,社交媒体上关于比特币减半的不确定性话题便会不断传播。这不仅仅是对一个价格点的讨论,更是对加密行业未来发展趋势的深入探讨。加密社区的成员们会依据这些信息来调整他们的投资策略。在一些加密社区活跃的城市,比如美国的硅谷,那里聚集了众多数字货币的爱好者与投资者,他们经常就市场走势进行交流。

价格波动若动摇了社区成员的信心,那么相关的区块链技术发展也会遭遇困难。因此,BTC价格的变动以及减半等议题在加密社区中引发的波动,其影响扩散至社区的运营和发展的方方面面。

最后有个问题想请教大家,面对现在这个看起来既复杂又多变的数字货币市场,假如你是投资者,你会怎样利用这些分析来调整你的投资计划?期待大家点赞并分享你们的观点。

暂无评论

发表评论